1、前言

Xilinx系列FPGA内置高速串行收发器,配有可配置的IP方便用户调用,按照速度等级和使用器件分别如下:

GTP:Artix7使用,最大线速率6.6Gbps,之前写过一篇GTP实现板间视频传输的文章,参考链接:GTP

GTX:Kintex7使用,最大线速率12.5Gbps,之前写过一篇GTX实现板间视频传输的文章,参考链接:GTX

GTH:ultrascale+系列的 GTH 收发器最高支持 16.3Gbps,本例程使用的器件是xczu7ev-ffvc1156-2-i;

本文详细描述了高端FPGA对GTH的回环测试的实现设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的高速信号传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

本设计提供2套工程源码:

工程1:GTH仿真工程;

工程1:GTH回环测试工程;

2、GTH 高速收发器介绍

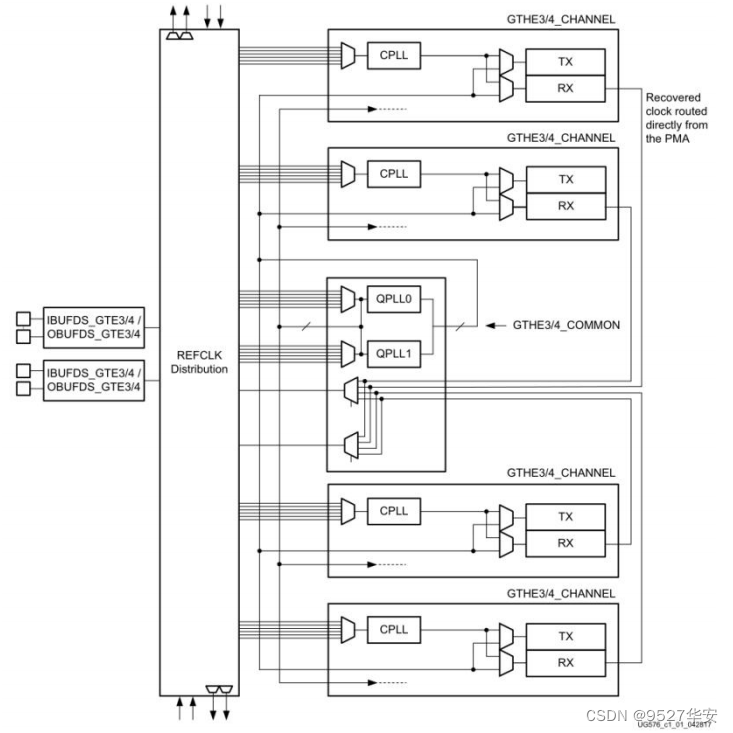

GTH 高速收发器结构

在 Ultrascale/Ultrascale+架构系列的 FPGA 中,GTH 高速收发器通常使用 Quad 来划分,一个 Quad 由四个GTHE3/4_CHANNEL 原语和一个 GTHE3/4_COMMON 原语组成。每个 GTHE3/4_COMMON 中包含两个 LC-tank pll(QPLL0 和 QPLL1)。只有在应用程序中使用 QPLL 时,才需要实例化 GTHE3/4_COMMON。

每个 GTHE3/4_CHANNEL 由一个 channel PLL(CPLL)、一个 transmitter,和一个 receiver 组成。一个参考时钟可以直接连接到一个 GTHE3/4_CHANNEL 原语,而不需要实例化 GTHE3/4_COMMON。

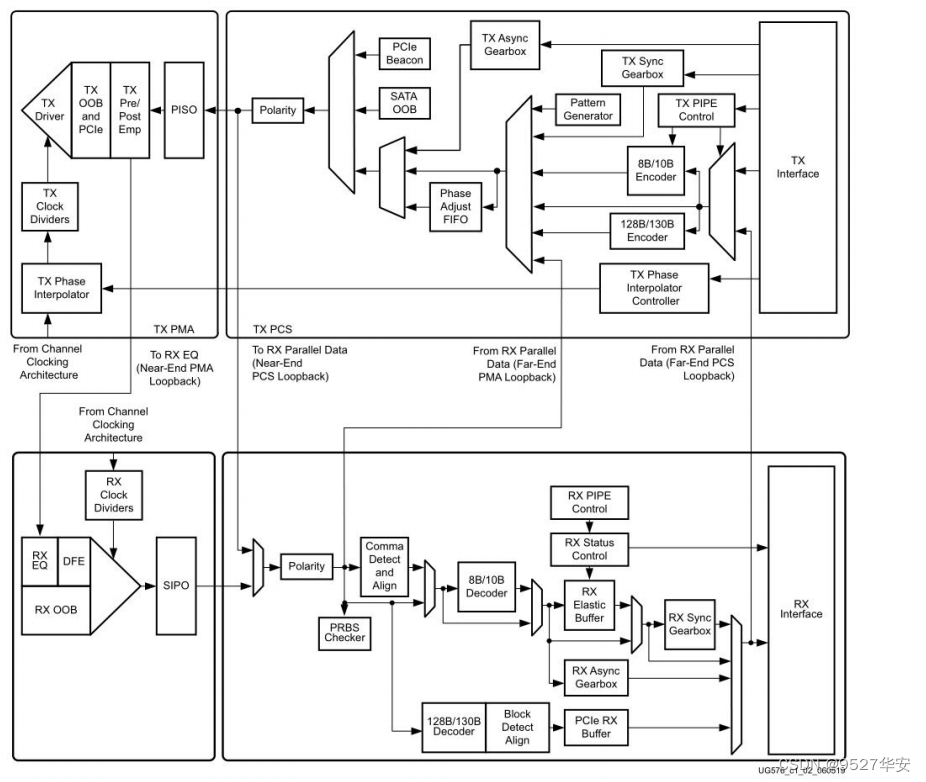

GTH 收发器的发送端和接收端功能是相互独立,都是由 Physical Media Attachment(物理媒介适配PMA)和Physical Coding Sublayer(物理编码子层 PCS)组成。PMA 内部集成了串并转换(PISO)、预加重、接收均衡、时钟发生器和时钟恢复等;PCS 内部集成了 8b/10b 编解码、弹性缓冲区、通道绑定和时钟修正等。

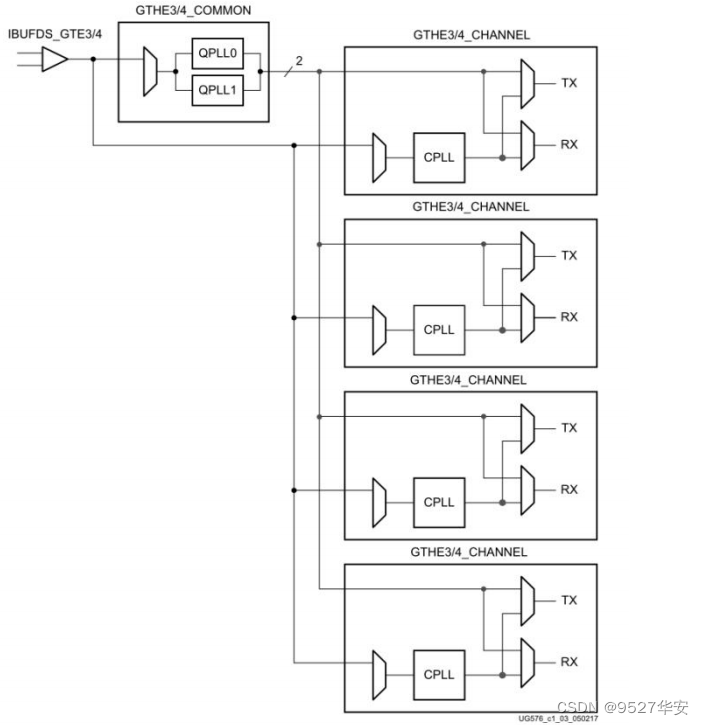

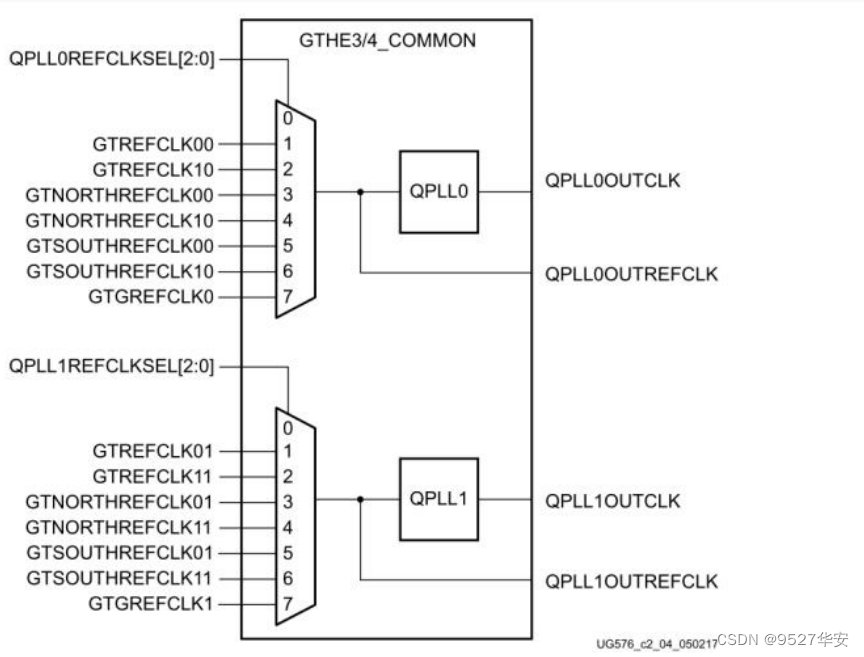

参考时钟的选择和分配

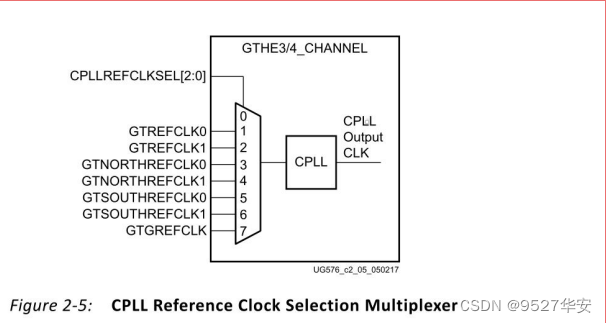

UltraScale 器件中的 GTH 收发器提供了不同的参考时钟输入选项。参考时钟选择架构支持 QPLL0、QLPLL1 和CPLL。从架构上讲,每个 Quad 包含四个 GTHE3/4_CHANNEL 原语,一个 GTHE3/4_COMMON 原语,两个专用的外部参考时钟引脚对,以及专用的参考时钟路由。如果使用到了高性能 QPLL,则必须实例化 GTHE3/4_COMMON,如下面 GTHE3/4_COMMON 时钟多路复用器结构的详细视图所示,在一个 Quad 中有 6 个参考时钟引脚对,两个本地参考时钟引脚对:GTREFCLK0或GTREFCLK1,两个参考时钟引脚对来自上面的两个Quads:GTSOUTHREFCLK0或 GTSOUTHREFCLK1,两个参考时钟引脚对来自下面的两个 Quads:GTNORTHREFCLK0 或 GTNORTHREFCLK1。

类似的,下面是 GTHE3/4_CHANNEL 原语中的参考时钟多路复用器结构的详细视图。

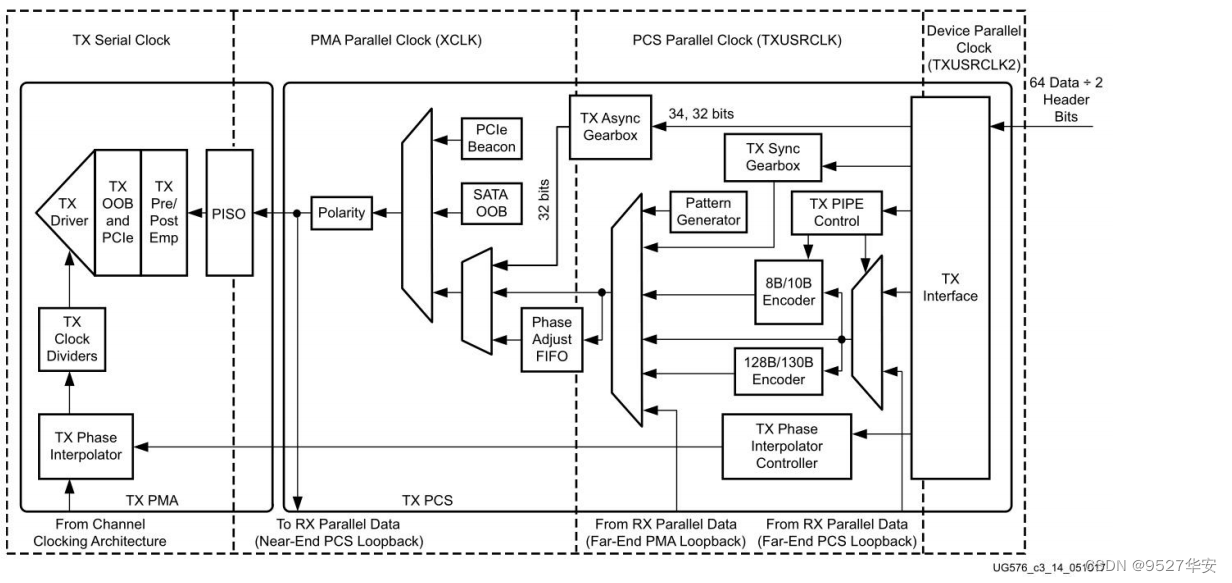

GTH 发送端

结合本节课的历程,来看一下 transmitter 端工作流程,并行数据从设备逻辑给到 TX 接口,首先进入物理编码子层(PCS),经过 8B/10B 编码器编码之后,进入一个发送缓存区 Phase Adjust FIFO。如下所示,GTH 收发器TX 数 据 路 径 有 两 个 用 于 PCS 的 内 部 并 行 时 钟 域 :PMA 并 行 时 钟 域 (XCLK) 和 PCS 并 行 时 钟 域(TXUSRCLK),如果要传输数据,XCLK 速率必须与 TXUSRCLK 速率匹配,并且必须解决两个时钟 域 之 间 的 相 位 差 。 GTH 发 送 端 提 供 了 一 个 TX buffer 和 一 个 TX 相 位 校 准 电 路 , 以 解 决 XCLK 和TXUSRCLK 域之间的相位差。推荐默认使用 TX Buffer,易于操作。如果对低延迟有严格要求则须旁路 TX buffer。当 TX buffer 被旁路时,使用 TX 相位校准电路去调整 XCLK 和 TXUSRCLK 域之间的相位差,以便将数据从 PCS 传输到 PISO。最后通过高速 Serdes 进行并串转换(PISO),经预/后加重,输出TX 驱动程序作为高速串行数据。

GTH 接收端

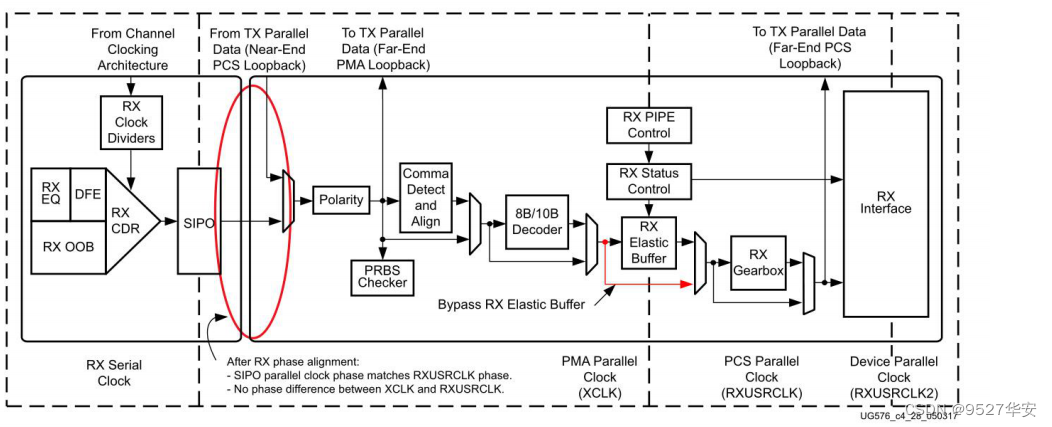

接下来看一下 Receiver 端工作流程,RX 接收到的信号会首先经过 RX 均衡器,均衡器的主要作用是用于补偿信号的高频损失, LPM 和 DFE 分别是两种不同模式的均衡器。

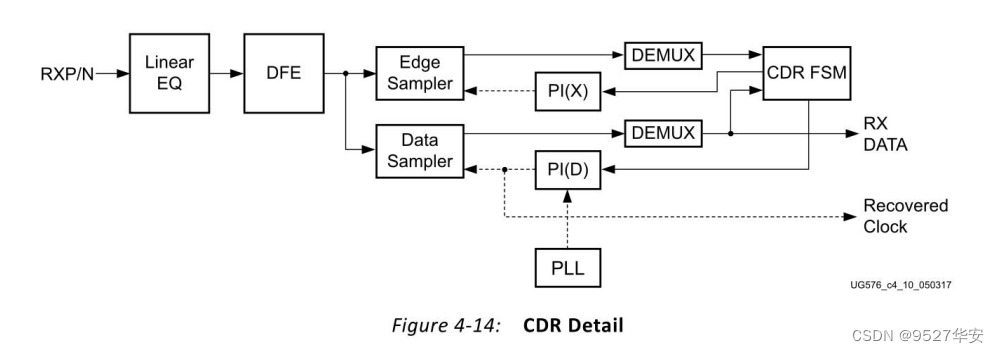

RX 的时钟数据恢复电路是图上图中的 RX CDR 模块,因为 GTH 传输不带随路时钟,因此在接收端必须去实现时钟恢复和数据恢复,时钟数据恢复电路下图所示:

GTHE3/4_CHANNEL 收发信机采用相位旋转 CDR 架构。传入数据首先经过接收机均衡阶段。均衡数据由边缘和数据采样器捕获。数据采样器捕获的数据被提供给 CDR 状态机和下游收发器块。CDR 状态机使用来自边缘和数据采样器的数据来确定传入数据流的相位,并控制相位插值器(pi)。边缘采样器的相位被锁定在数据流的过渡区域,而数据采样器的相位被定位在数据眼的中间,CPLL 或 QPLL 为相位插补器提供基准时钟。相位插补器反过来产生良好的、均匀间隔的采样相位,以允许 CDR 状态机有良好的相位控制。

数据经过 CDR 之后进行串并转换,这里的 Polarity 是用来进行极性控制的,如果传入的数据是 PRBS,那么接下来会使用内嵌的 PRBS 检查器进行 check,xilinx 官方提供了四种不同的伪随机序列生成器可供用户选择,PRBS checker 用来测试信号的完整性。如果传入的是 8b10b 编码后的用户数据,那么接下来就会对传出的数据进行边界对齐和 8b10b 的解码。

最后是 RX elastic buffer 这个部分,如上图所示,GTH 收发器 RX 数据路径有两个用于 PCS 的内部并行时钟域:PMA 并行时钟域(XCLK)和 PCS 并行时钟域(RXUSRCLK),为了接收数据,PMA 并行速率必须足够接近

RXUSRCLK 速率,并且必须解决两个时钟域之间的相位差。GTH 收发器包含一个 RX elastic buffer,以解决 XCLK和 RXUSRCLK 域之间的差异。当 RX elastic buffer 被旁路时,RX 相位校准电路用于调整 SIPO 并行时钟域和 RXXCLK 域之间的相位差,以实现从 SIPO 到 PCS 的可靠数据传输,最后输出给 RX 外部接口。要特别注意一下的是RX elastic buffer 还具有时钟纠正和通道绑定功能。

3、vivado工程详解

开发板:Zynq ultrascale+xczu7ev-ffvc1156-2-i;

开发环境:vivado2021.1,2021.1以上版本均可打开,升级一下IP即可使用;

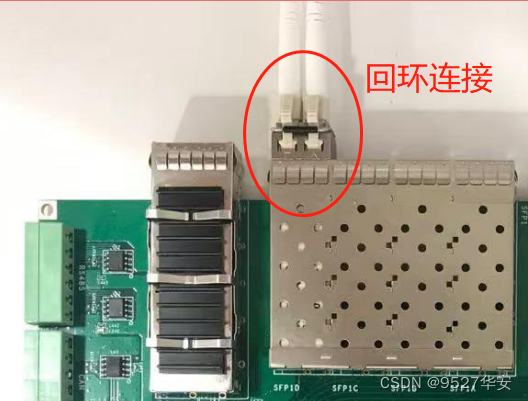

输入/输出:SFP接口的GTX对插回环;

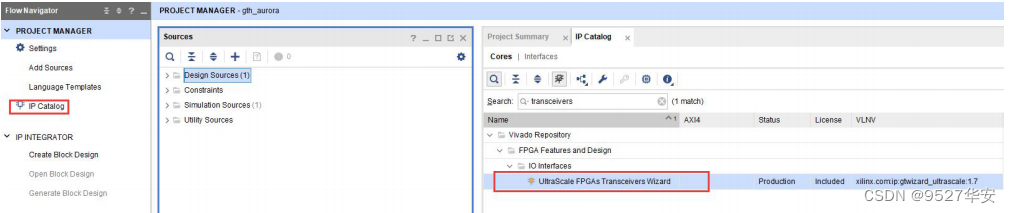

首先创建一个工程,添加 UltraScale FPGAs Transceivers Wizard IP;

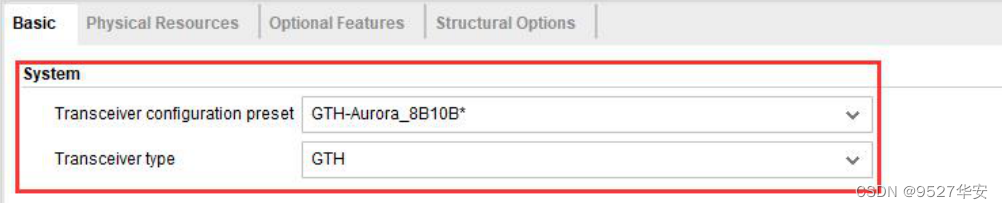

这 里 的 预 设 配 置 选 择 GTH-aurora_8B10B 即 可 。 串 行 收 发 器 类 型 取 决 于 使 用 的 具 体 设 备 , 以MZU04A 板卡为例,它的 SFP+仅支持 GTH 类型。

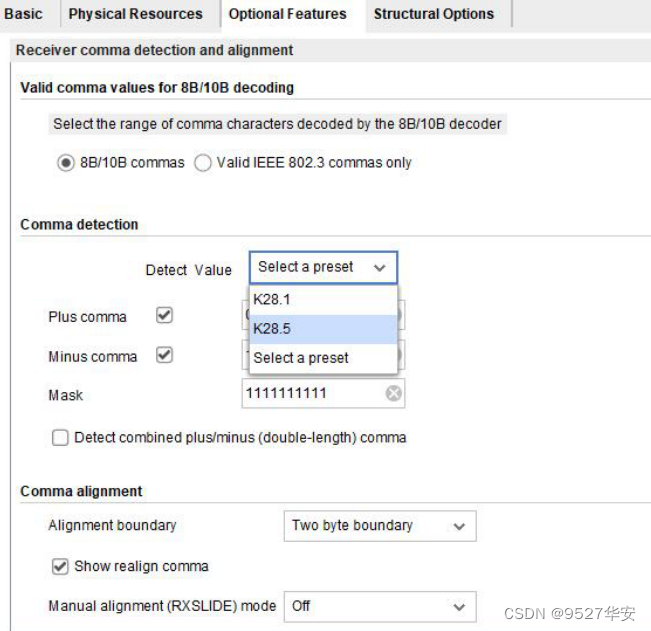

接收端边界对齐和 comma 检测:

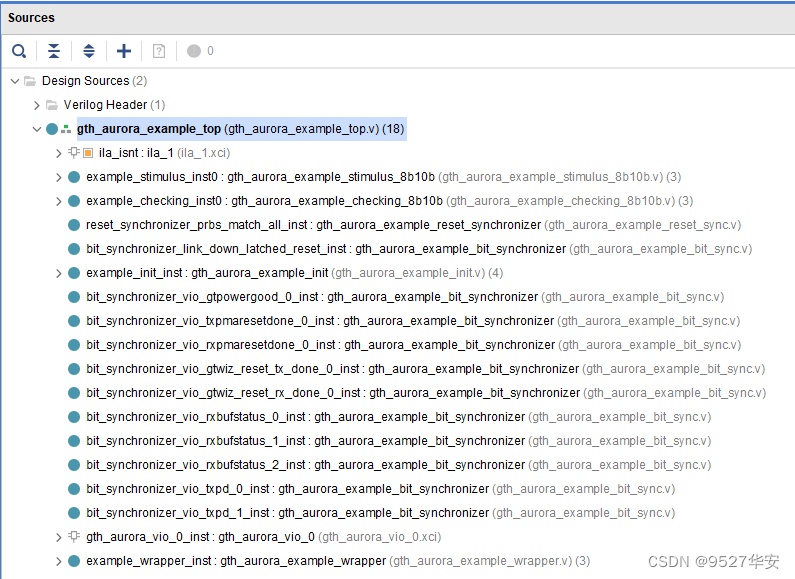

工程代码架构如下:

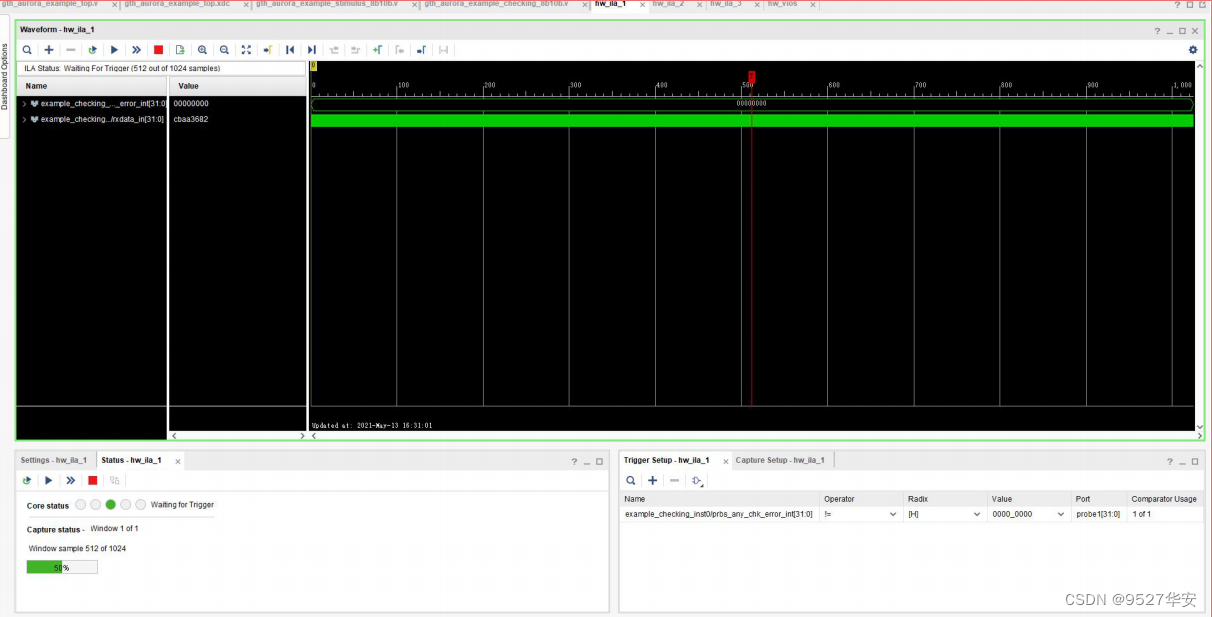

4、上板调试验证

编译完工程之后下载程序,验证光纤接口 8b10b 回环实验。下载完成后查看 ILA 的波形,当检测模块中的

prbs_any_chk_error_int 信号一直为 0,说明光纤接口 8b10b 环回实验下载验证成功。

5、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

今天的文章高端Zynq ultrascale+使用GTH回环测试 提供2套工程源码和技术支持「建议收藏」分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/86118.html