SOI技术简介、SIMOX技术、BESOI技术、Smart-Cut技术详见:《【半导体先进工艺制程技术系列】SOI技术(上)》

PD-SOI技术、翘曲效应、寄生双极晶体管效应、自加热效应、体接触详见:《【半导体先进工艺制程技术系列】SOI技术(中)》

FD-SOI工艺技术

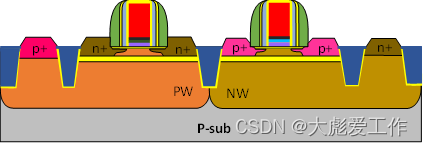

PD-SOI不但存在浮体效应,并且随着SOI工艺技术发展到纳米级,PD-SOI器件的短沟道效应变得越来越严重,而对于FD-SOI器件,当器件工作在饱和区时,硅薄膜是全耗尽的,源和体之间的势垒很小,空穴很容易在源区被复合而不发生累积,所以浮体效应对FD-SOI器件的影响非常小,另外FD-SOI器件源漏极很薄的结深可以减小源漏极耗尽层横向扩散的宽度,从而有效的抑制短沟道效应,FD-SOI器件被广泛应用于纳米级工艺。

FD-SOI除了可以改善浮体效应和短沟道效应外,还具有许多其他方面的优点,包括具有独特的背面偏置能力,低的电源电压(最小的电源电压接近阈值电压,可以达到0.4V),低的漏电流,低的寄生电容,强的抵御辐射的能力,强的晶体管匹配特性和高的器件工作速度等。这些优点使FD-SOI被应用在智能手机处理器、自动驾驶芯片、物联网芯片、通讯收发器和汽车电子等应用。

FD-SOI工艺流程

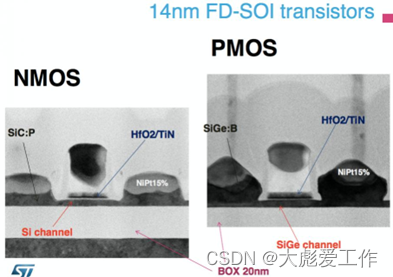

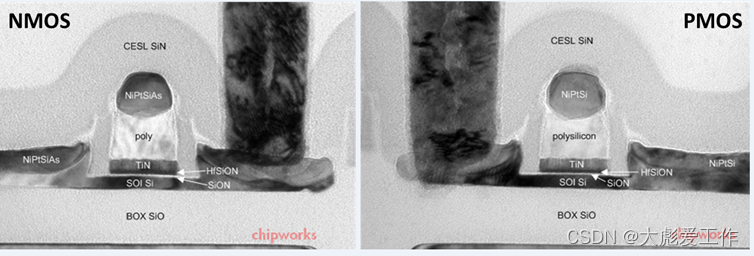

FD-SOI的工艺技术与MOSFET平面工艺制程是兼容的,FD-SOI的工艺技术的前段工艺制程采用了先栅HKMG和应变硅技术,后段依然是大马士革结构的铜制程。

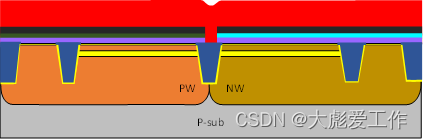

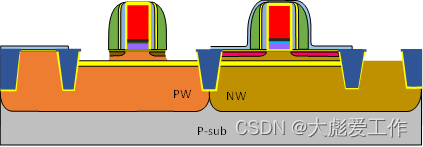

1.SOI衬底制备。

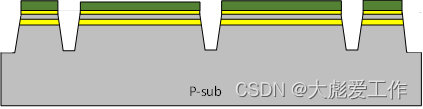

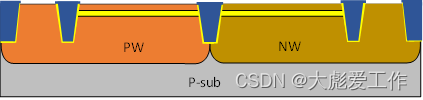

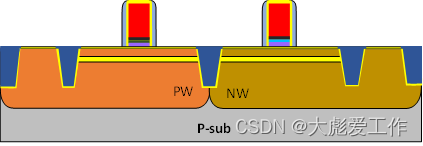

2.淀积SiO2和Si3N4,并通过光刻和刻蚀形成STI;

3.通过HDP CVD淀积SiO2,然后通过CMP平坦化;

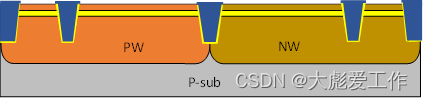

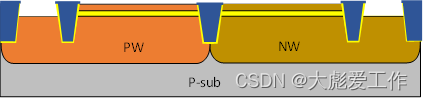

4.去除SiO2和Si3N4,并通过光刻和离子注入形成NW和PW;

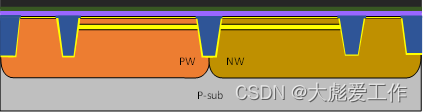

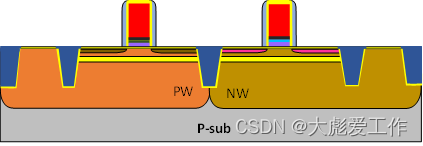

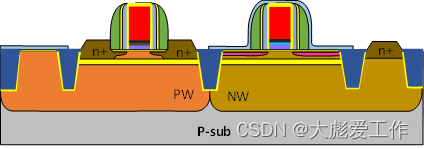

5.通过光刻和刻蚀,去除NW和PW接触的氧化埋层;

6.通过选择性外延生长PW和NW的接触区;

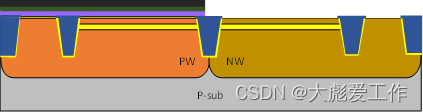

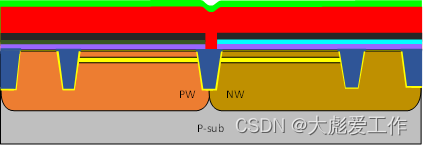

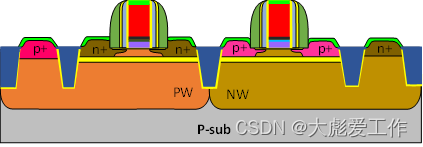

7.淀积SiON,HfSiON,La2O3和TiN金属覆盖层;

8.通过光刻和刻蚀去除PMOS区域的栅介质层;

9.淀积SiON,HfSiON,Al2O3和TiN金属覆盖层,并通过光刻和刻蚀去除NMOS区域二次淀积的栅介质层;

10.淀积多晶硅栅极。

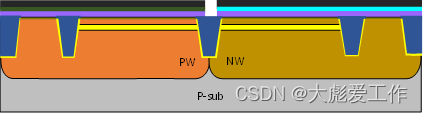

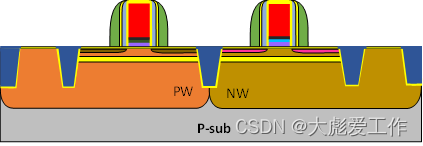

11.通过LPCVD淀积SiO2和SiON硬掩膜版层;

12.通过光刻和刻蚀形成硬掩膜版层;

13.通过刻蚀形成栅极;

14.淀积SiO2和Si3N4,并通过刻蚀形成隔离侧墙;

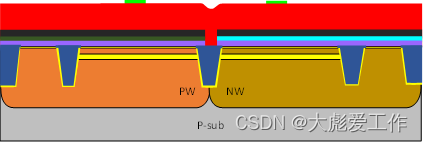

15.通过光刻和离子注入形成LDD结构;

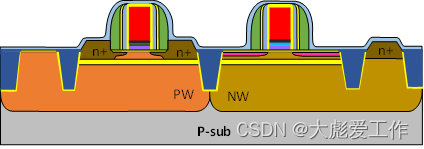

16.淀积SiO2,Si3N4和SiO2,并通过刻蚀形成第二重隔离侧墙;

17.利用LPCVD淀积一层的SiO2氧化层,作为SiGe外延生长的阻挡层;

18.通过光刻和刻蚀,去除NMOS区域的SiO2氧化层。再通过选择性回刻技术刻蚀硅衬底,在n有源区形成凹槽;

19.通过外延生长形成应变硅材料SiC的n型有源区;

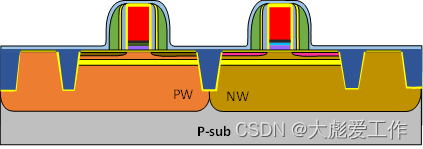

20.利用LPCVD淀积一层的SiO2氧化层,作为SiGe外延生长的阻挡层;

21.通过光刻和刻蚀,去除PMOS区域的SiO2氧化层。再通过选择性回刻技术刻蚀硅衬底,在p有源区形成凹槽;

22.通过外延生长形成应变硅材料SiGe的p型有源区;

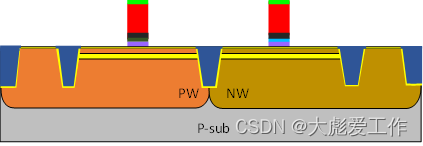

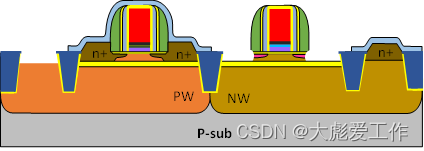

23.形成Salicide。

FD-SOI工艺技术是利用外延生长技术使源和漏有源区凸起,同时进行源和漏掺杂,因为FD-SOI的有源区厚度很薄,通过外延生长技术使源和漏有源区凸起,可以增加有源区的厚度和表面积,从而形成更厚的Salicide,减小源和漏的接触电阻。在PMOS源和漏有源区外延生长SiGe应变材料和在NMOS源和漏区外延生长SiC应变材料可以在器件沟道产生应力,提高载流子速度,最终提高FD-SOI器件的速度。

相关内容

《【半导体先进工艺制程技术系列】应变硅工艺技术》

《【半导体先进工艺制程技术系列】HKMG工艺技术(上)》

《【半导体先进工艺制程技术系列】HKMG工艺技术(下)》

《【半导体先进工艺制程技术系列】SOI技术(上)》

《【半导体先进工艺制程技术系列】SOI技术(中)》

今天的文章半导体sorter_半导体制程简介ppt分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/89026.html