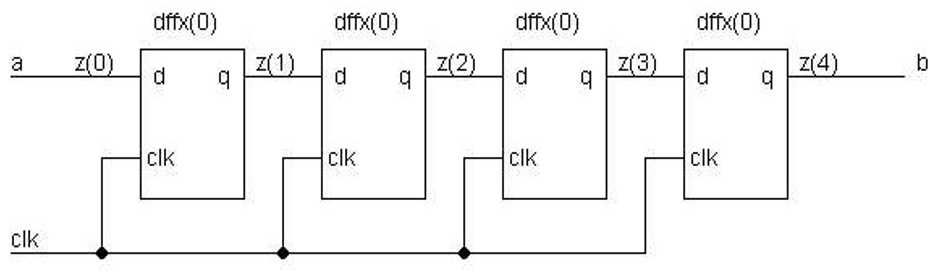

1.电路图

移位寄存器:具有存储代码,移位功能

移位:寄存器里所储存的代码能够在移位脉冲的作用下,依次左移或右移

2.VHDL语言

2.1 D触发器

library ieee;

use ieee.std_logic_1164.all;

entity dff1 is

port(

clk,d:in std_logic;

q:out std_logic

);

end dff1;

architecture behavior of dff1 is

begin

process(clk) --进程语句以及敏感信号

begin

if rising_edge(clk) then q <= d; --rising_edge 是非常严格的上升沿,必须从0到1

end if;

end process;

end behavior;

2.2 4位移位寄存器

描述1

library ieee;

use ieee.std_logic_1164.all;

entity shift_reg is

port (a,clk : in std_logic;

b : out std_logic);

end shift_reg;

architecture behave of shift_reg is

component dff

port(d,clk:in std_logic;

q:out std_logic);

end component;

signal z:std_logic_vector(0 to 4);

begin

dff1:dff port map(a,clk,z(1));

dff2:dff port map(z(1),clk,z(2));

dff3:dff port map(z(2),clk,z(3));

dff4:dff port map(z(3),clk,b);

end behave;

描述2

begin

z(0)<=a;b<=z(4);

dff1:dff port map(z(0),clk,z(1));

dff2:dff port map(z(1),clk,z(2));

dff3:dff port map(z(2),clk,z(3));

dff4:dff port map(z(3),clk,z(4));

end behave;

描述3

begin

z(0)<=a;b<=z(4);

g1:for i in 0 to 3 generate --for generate语句

dffx:dff port map(z(i),clk,z(i+1));

end generate;

end behave;

今天的文章VHDL——4位移位寄存器分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/12605.html